Saarland University Faculty of Natural Sciences and Technology I Department of Computer Science Master's Program in Computer Science

## - Master's Thesis —

# Realtime Optical Flow Algorithms on the Cell Processor

# Pascal Gwosdek

2008-4-14

SupervisorProf. Dr. Joachim WeickertAdvisorDr. Andrés BruhnReviewersProf. Dr. Joachim WeickertProf. Dr. Reinhard Wilhelm

## Affidavit

I hereby declare that this master's thesis has been written only by the undersigned and without any assistance from third parties.

Furthermore I confirm that no sources have been used in the preparation of this thesis other than those indicated in the thesis itself.

Saarbrücken, 2008-4-14

## **Declaration of Consent**

Herewith I agree that this thesis will be made available through the library of the Computer Science Department. This consent explicitly includes both the printed, as well as the electronic form attached to the last page of this thesis.

I confirm that the electronic and the printed version are of identical content.

Saarbrücken, 2008-4-14

### Abstract

The estimation of motion information in terms of optical flow is nowadays a common instrument for many applications in Computer Vision. Relying on the solution of a linear or nonlinear equation system, those algorithms are still comparably slow, even though realtime setups can already been established for smaller images. Modern processor layouts show promise to accelerate this procedure, or to be capable of larger problem sizes.

In this thesis, the potential of the Cell Broadband Engine built into the Sony Playstation 3 video console is explored and its applicability for the optic flow problem evaluated. After creating a setup for scientific computing on the device, different parallelization attempts distributing computational load to seven available cores are compared with each other. Hereby, specific characteristics of the Cell processor layout are addressed and the impact of specific acceleration techniques optimized for the architecture is appraised. Efficient solvers known from both sequential and other parallel architectures, namely Block SOR, Red-Black SOR and Full Multigrid, are tested for their performance on the novel platform, whereby particular attention is paid to memory management and synchronization among the different cores. It is shown that by applying hardware-specific optimizations, optical flow algorithms can be significantly accelerated compared to a traditional processor. Eventually, an interactive real-time configuration with graphical output is described and tested, and the capabilities of the Playstation 3 are compared and discussed with respect to this setting.

## Acknowledgements

I would like to express my sincere thanks to my advisor Dr. Andrés Bruhn and my supervisor Prof. Dr. Joachim Weickert for their excellent mentoring and support during the development of this thesis. Their encouragement and the friendly atmosphere among colleagues in the Mathematical Image Analysis Group greatly assisted me in my work. I also like to thank Prof. Dr. Reinhard Wilhelm for consenting to review my thesis.

Special thanks also go to my parents and my sister who enabled me to perform my studies as I did and who therefore also significantly contributed to the success I have enjoyed so far.

# Contents

| 1 | Intro | oduction 1                             |  |  |  |  |  |  |  |  |  |

|---|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|

|   | 1.1   | Motivation                             |  |  |  |  |  |  |  |  |  |

|   | 1.2   | Goals                                  |  |  |  |  |  |  |  |  |  |

|   | 1.3   | Contents                               |  |  |  |  |  |  |  |  |  |

|   | 1.4   | Typographic Conventions    3           |  |  |  |  |  |  |  |  |  |

| 2 | Sony  | Sony Playstation 3 5                   |  |  |  |  |  |  |  |  |  |

|   | 2.1   | History 55                             |  |  |  |  |  |  |  |  |  |

|   | 2.2   | Hardware                               |  |  |  |  |  |  |  |  |  |

|   | 2.3   | Scientific Interest                    |  |  |  |  |  |  |  |  |  |

| 3 | Cell  | Broadband Engine 9                     |  |  |  |  |  |  |  |  |  |

|   | 3.1   | History                                |  |  |  |  |  |  |  |  |  |

|   | 3.2   | Layout Overview                        |  |  |  |  |  |  |  |  |  |

|   | 3.3   | Pipelining                             |  |  |  |  |  |  |  |  |  |

|   | 3.4   | Power Processor Element                |  |  |  |  |  |  |  |  |  |

|   |       | 3.4.1 Architecture Overview            |  |  |  |  |  |  |  |  |  |

|   |       | 3.4.2 PPU as an Application Controller |  |  |  |  |  |  |  |  |  |

|   | 3.5   | Synergistic Processor Element          |  |  |  |  |  |  |  |  |  |

|   |       | 3.5.1 Architecture Overview            |  |  |  |  |  |  |  |  |  |

|   |       | 3.5.2 Local Store                      |  |  |  |  |  |  |  |  |  |

|   |       | 3.5.3 AltiVec SIMD                     |  |  |  |  |  |  |  |  |  |

|   |       | 3.5.4 Restrictions                     |  |  |  |  |  |  |  |  |  |

|   |       | 3.5.5 SPU Intrinsics                   |  |  |  |  |  |  |  |  |  |

|   |       | 3.5.6 Synchronization                  |  |  |  |  |  |  |  |  |  |

|   | 3.6   | Element Interconnect Bus               |  |  |  |  |  |  |  |  |  |

|   | 3.7   | Processor Bus Interface                |  |  |  |  |  |  |  |  |  |

|   | 3.8   | RAM Interface                          |  |  |  |  |  |  |  |  |  |

|   | 3.9   | Binary Layout                          |  |  |  |  |  |  |  |  |  |

|   | 3.10  | Summary                                |  |  |  |  |  |  |  |  |  |

#### CONTENTS

| 4 | Deve | lopment Platform 2                                   | 9 |

|---|------|------------------------------------------------------|---|

|   | 4.1  | Linux                                                | 9 |

|   |      | 4.1.1 Installation                                   | 0 |

|   |      | 4.1.2 Adoption for Scientific Computing              | 1 |

|   |      | 4.1.3 Kernel Support for Huge TLB Pages              | 1 |

|   |      | 4.1.4 Cell Broadband Engine Specific Characteristics | 2 |

|   | 4.2  | Compiler and Toolchain                               | 3 |

|   | 4.3  | IBM Full-System Simulator                            | 4 |

|   | 4.4  | Debugging                                            | 5 |

|   |      | 4.4.1 GDB                                            | 6 |

|   |      | 4.4.2 Data Display Debugger (DDD) 3                  | 8 |

|   |      | 4.4.3 Other Tools                                    | 8 |

|   |      | 4.4.4 Full-System Simulator                          | 9 |

|   |      | 4.4.5 Summary                                        | 0 |

|   |      |                                                      |   |

| 5 | -    | cal Flow 4                                           |   |

|   | 5.1  | Motivation                                           |   |

|   | 5.2  | Horn and Schunck Model                               |   |

|   | 5.3  | Motion Tensor Notation                               | - |

|   | 5.4  | Combined Local-Global Method                         | - |

|   | 5.5  | Minimization                                         | - |

|   | 5.6  | Discretization                                       | - |

|   | 5.7  | Sequential Implementation                            | 7 |

| 6 | Suco | essive Over-Relaxation 4                             | 9 |

| Ū | 6.1  | Theory                                               |   |

|   |      | 6.1.1 Gaussian Elimination                           | 9 |

|   |      | 6.1.2 Iterative Solvers                              | - |

|   |      | 6.1.3 Jacobi Method                                  | - |

|   |      | 6.1.4 The Gauss-Seidel Method                        |   |

|   |      | 6.1.5 Successive Over-Relaxation                     |   |

|   | 6.2  | Reference Implementation on Pentium 4                |   |

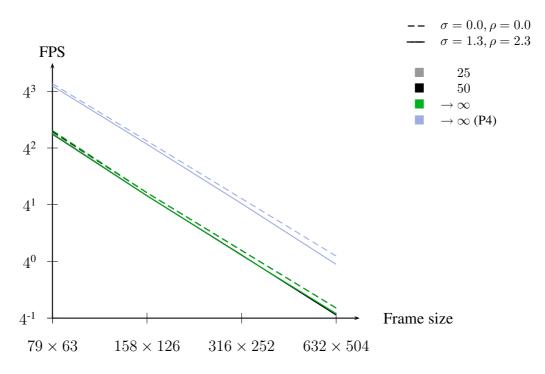

|   | 0.1  | 6.2.1 Impact of Different Image Sizes                |   |

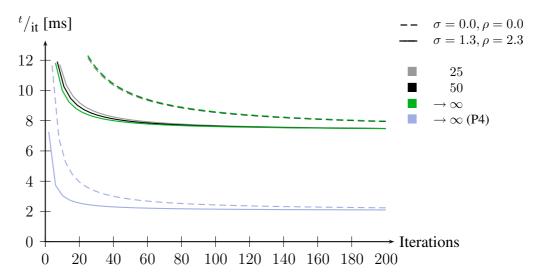

|   |      | 6.2.2 Impact of Different SOR Iteration Counts       |   |

|   | 6.3  | Performance on the PPU                               |   |

|   | 0.0  | 6.3.1 Impact of Different Image Sizes                |   |

|   |      | 6.3.2 Impact of Different SOR Iteration Counts       |   |

|   | 6.4  | Block SOR                                            |   |

|   |      | 6.4.1 Motivation and Idea                            |   |

|   |      | 6.4.2 Synchronization                                |   |

|   |      | 6.4.3 Benchmarks                                     |   |

|   |      | 6.4.4 Discussion                                     |   |

|   | 6.5  | Red-Black SOR   7                                    |   |

|   |      | 6.5.1  | Motivation                                          |

|---|------|--------|-----------------------------------------------------|

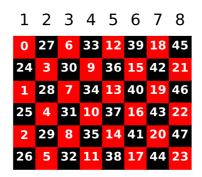

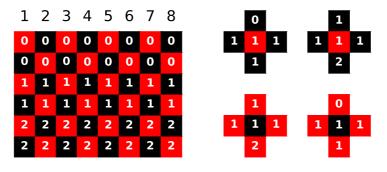

|   |      | 6.5.2  | Reordering                                          |

|   |      | 6.5.3  | Memory Representation                               |

|   |      | 6.5.4  | Smoothing                                           |

|   |      | 6.5.5  | Setup of the Equation System                        |

|   |      | 6.5.6  | Solver                                              |

|   |      | 6.5.7  | Synchronization                                     |

|   |      | 6.5.8  | Benchmarks                                          |

|   | 6.6  | Red-B  | lack SOR with Joint Kernels                         |

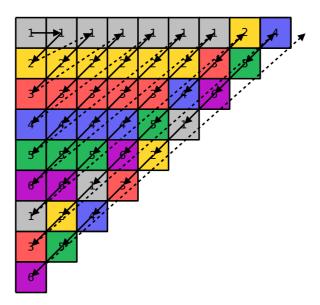

|   |      | 6.6.1  | Reordering                                          |

|   |      | 6.6.2  | Synchronization                                     |

|   |      | 6.6.3  | Benchmarks                                          |

|   |      | 6.6.4  | Discussion                                          |

| 7 | Full | Multig | rid 97                                              |

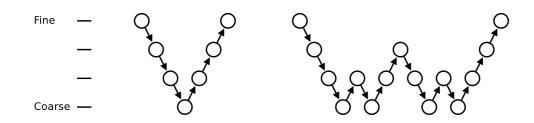

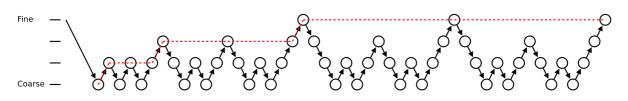

|   | 7.1  | U      | 97                                                  |

|   | ,    | 7.1.1  | Multigrid Methods                                   |

|   |      | 7.1.2  |                                                     |

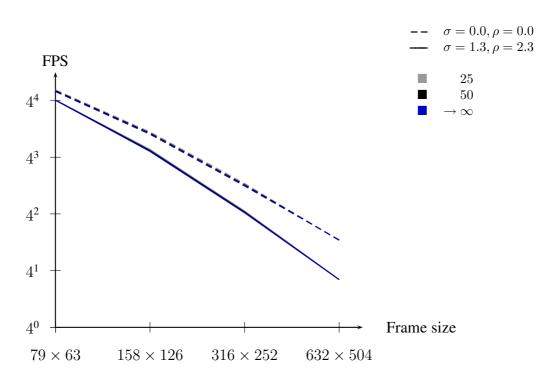

|   | 7.2  |        | nce Implementation on Pentium 4                     |

|   |      | 7.2.1  | Impact of Different Image Sizes                     |

|   | 7.3  |        | nance on the PPU                                    |

|   |      | 7.3.1  | Impact of Different Image Sizes                     |

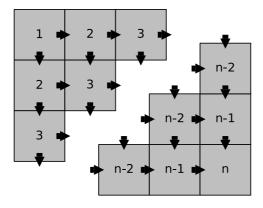

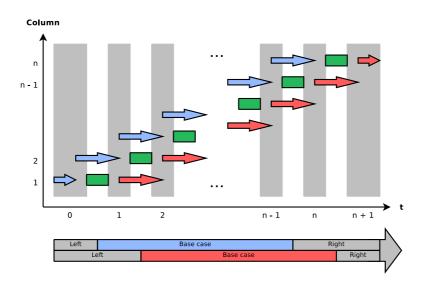

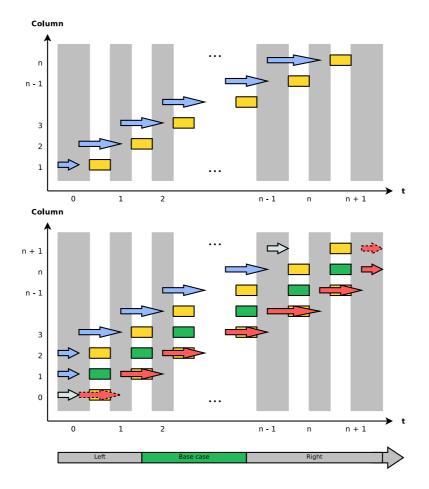

|   | 7.4  | Toward | ls a Parallel Variant                               |

|   | 7.5  |        | Store Based Variant                                 |

|   | 7.6  | Memor  | ry Representation                                   |

|   | 7.7  |        | nentation of the SPU Kernel                         |

|   |      | 7.7.1  | General Structure                                   |

|   |      | 7.7.2  | Resampling                                          |

|   |      | 7.7.3  | Relaxation Steps                                    |

|   |      | 7.7.4  | Initialization                                      |

|   |      | 7.7.5  | Residual Computation                                |

|   |      | 7.7.6  | Matrix Addition                                     |

|   |      | 7.7.7  | Motion Tensor Computation                           |

|   |      | 7.7.8  | Equation System Setup                               |

|   |      | 7.7.9  | Presmoothing                                        |

|   |      | 7.7.10 | Debugging                                           |

|   | 7.8  | Binary | Optimization                                        |

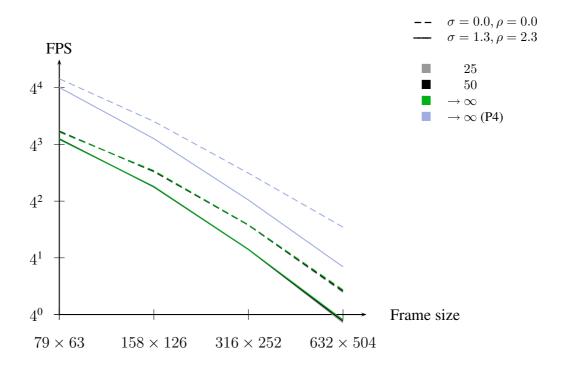

|   | 7.9  | Benchi | narks                                               |

|   |      | 7.9.1  | Impact of Different Image Sizes                     |

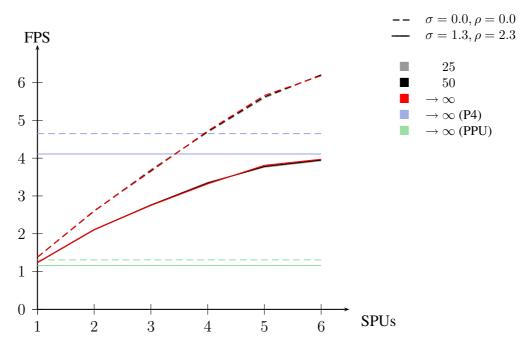

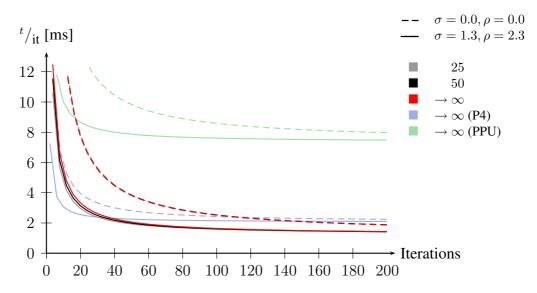

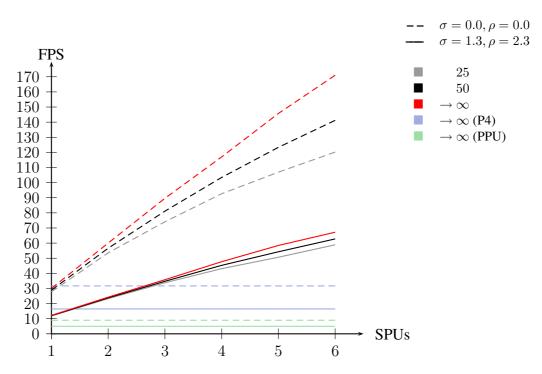

|   |      | 7.9.2  | Scaling with the Number of SPUs                     |

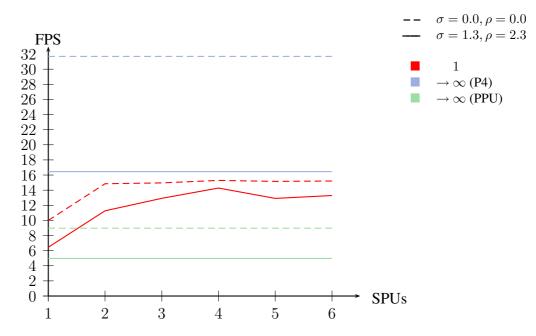

|   |      | 7.9.3  | Scaling with the Number of SPUs for Small Intervals |

|   | 7.10 | Discus | sion                                                |

#### CONTENTS

| 8          | Inte                       | ractive Realtime Setup     | 129 |  |  |  |  |  |  |  |  |

|------------|----------------------------|----------------------------|-----|--|--|--|--|--|--|--|--|

|            | 8.1                        | Installation of the Webcam | 129 |  |  |  |  |  |  |  |  |

|            | 8.2                        | Adoption of the Program    | 130 |  |  |  |  |  |  |  |  |

|            | 8.3                        | Results                    | 132 |  |  |  |  |  |  |  |  |

|            | 8.4                        | Summary                    | 133 |  |  |  |  |  |  |  |  |

| 9          | Conclusion and Future Work |                            |     |  |  |  |  |  |  |  |  |

|            | 9.1                        | Overview                   | 135 |  |  |  |  |  |  |  |  |

|            | 9.2                        | Conclusion                 | 136 |  |  |  |  |  |  |  |  |

|            | 9.3                        | Future Work                | 136 |  |  |  |  |  |  |  |  |

| References |                            |                            |     |  |  |  |  |  |  |  |  |

# **Chapter 1**

## Introduction

### **1.1 Motivation**

In Computer Vision, one of the main challenges is the automatic extraction of motion information from image sequences. Without any prior knowledge about the captured scene, one often not only wants to purely identify movements in a scene, but also likes to know in which direction an object is travelling, and at which velocity.

Since the position and own motion of the camera is usually not known as well, one often confines oneself to the relative movements of objects with respect to the camera, and describes these displacements between two subsequent frames of the sequence with a dense vector field, the *optical flow* field.

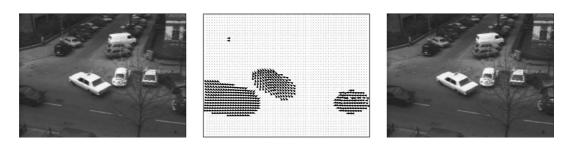

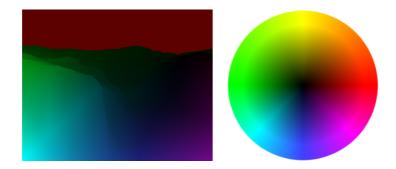

Nowadays, optical flow fields find use in a broad range of applications, like for video compression or enhancement, object tracking, driver assistance systems, autonomous navigation of robots, or video surveillance [16]. One example for such application is depicted in Figure 1.1, where the movement of several objects in a traffic sequence is appraised.

Several algorithms to estimate the optical flow have been proposed in the past. Many of them belong to the so-called *variational approaches*, which formulate the process as a minimization process of an energy functional [27]. Though these methods are among the most

**Figure 1.1: Left** and **right**: Frames 10 and 11 of the well-known Hamburg Taxi sequence by Nagel. **Middle**: Estimated optical flow field, visualized with arrows pointing in direction of the motion. **Authors:** J. Weickert and C. Schnörr [67].

accurate methods available, they are also quite expensive to compute, because they require large systems of equations with millions of unknowns to be solved.

By numerical improvements, these algorithms could already be accelerated by two orders of magnitude, and for smaller image sizes, even realtime performance have been achieved on standard PCs [14]. For various time-critical applications however, these results are still not sufficient.

Modern parallel processor architectures promise a remedy to this problem, since they offer a higher performance by distributing the algorithm to several cores. Particularly, the Cell Broadband Engine built into the Sony Playstation 3 video console, one of the cheapest parallel computers on the market, has already been used for many scientific purposes: Current application fields include for instance matrix multiplications [18], the implementation of diffusion processes and the Fast Fourier Transform [71], an entire raytracer implementation [7], or partial differential equation based video compression [44].

#### **1.2 Goals**

This thesis is meant to evaluate the applicability of the Cell Broadband Engine for the optic flow problem, and should in particular test whether it is eligible to accelerate common algorithms significantly.

For this purpose, a Sony Playstation 3 video console shall be prepared for scientific use, and a development platform allowing to create, debug and execute new programs should be set up. By a closer study of the Cell Broadband Engine's characteristics, a general impression of the underlying architecture should be gained and ways and means shall be considered to use these peculiarities for advanced optimizations.

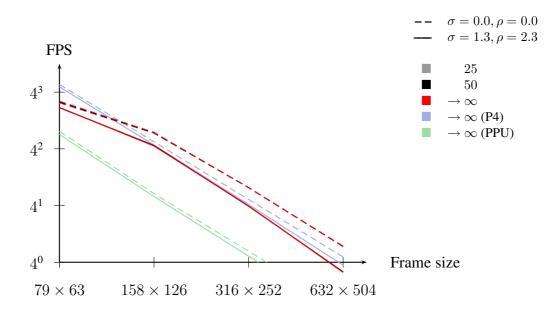

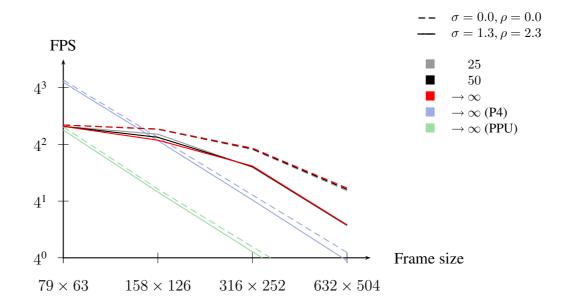

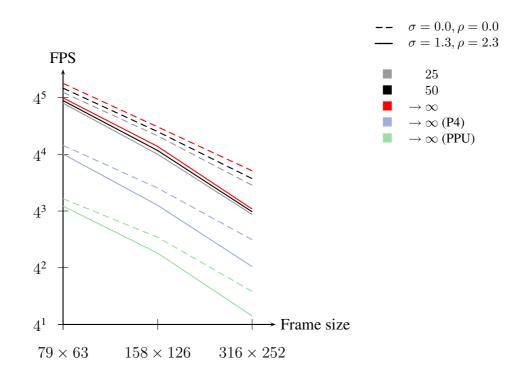

Within this framework, several efficient algorithms with prospect of realtime performance shall be suitably parallelized for the application on the Cell processor. By optimizing them for this architecture, their runtime performance is to be be enhanced best possible, compared to a sequential implementation on an Intel Pentium 4 processor. Particular attention should thereby additionally be paid to the performance with respect to different image sizes, especially towards larger frame dimensions.

Since the experiments are going to be performed on a Playstation 3, this special platform shall as well be attentively regarded, and related advantages or disadvantages should be carved out accordingly.

### **1.3** Contents

The structure of this thesis is as follows. In Chapter 2, an introduction to the Playstation 3 video console is going to be given, and its hardware specifications are described. Proximately, the Cell Broadband Engine Processor is in detail presented in Chapter 3, whereby special attention is paid to the cores used for high performant computations. In particular, their specific characteristics, as well as their technical means of interaction and synchronization are going to

be explored. Chapter 4 is finally going to conclude this rather hardware-oriented episode with information about how to enable the Playstation 3 for scientific computing. This covers both the installation of a multi-purpose operating system and compiler toolchain, as well as a discussion about the opportunities this setting offers with respect to development and debugging of new programs.

Subsequently, a short introduction into the optical flow problem is given in Chapter 5, and the CLG optical flow model by Bruhn *et al.*, which is going to be used throughout this thesis, is being explained [17].

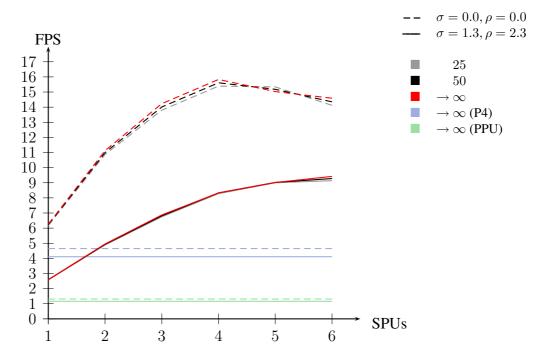

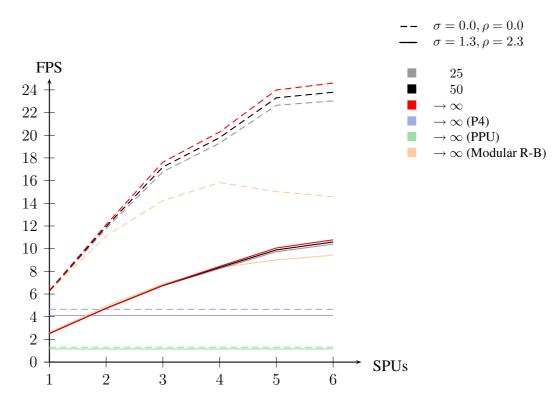

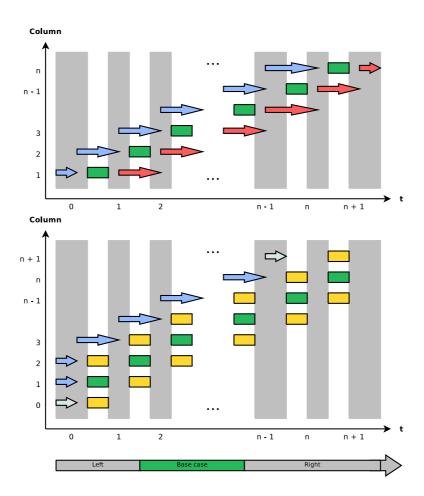

Chapter 6 introduces the so-called *Successive Over-Relaxation* method as a simple solver for equation systems arising in context of the optical flow computation. Beginning with a theoretical introduction and an appraisal of the performance of existing implementations, two parallel implementations are going to be presented aiming at an acceleration of the computation process. In a last experiment, the second algorithm is implemented in an alternative concrete realization to reduce constant expenses. The effectiveness of all parallelization attempts is thereby immediately evaluated in terms of performance benchmarks.

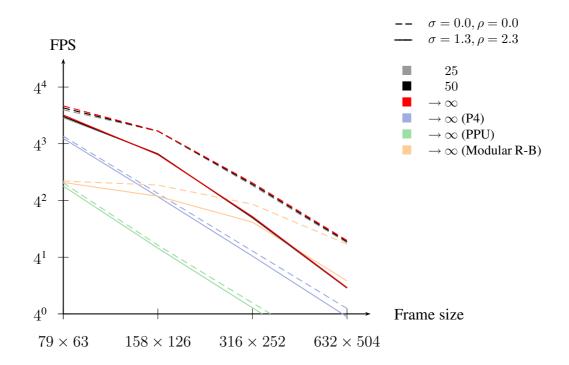

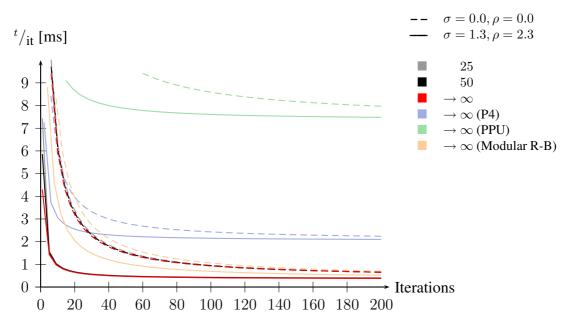

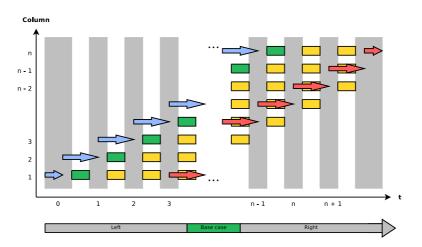

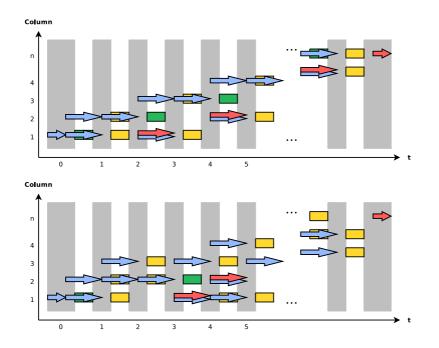

In Chapter 7, a Multigrid solver is used, which is known for a high performance and fast convergence on sequential architectures. Like for the previous method, the theory behind this idea is briefly formulated, and reference benchmarks are issued on a sequential implementation. For the optimized version, a new parallelization concept is being presented and a framework is introduced that allows both high performance and simplicity in development and maintenance. Again, this newly devised version is being evaluated with respect to runtime performance, and is compared to the results achieved on traditional hardware.

Eventually, the developed algorithms are tested in an interactive realtime setting, including webcam input, processing of the yielded frames and output of the results in an appealing manner. Chapter 8 hence evaluates the general qualification of the Playstation 3 for such purpose, and shows advantages and disadvantages of this configuration.

Finally, the prior units are concluded in Chapter 9, and a recapitulatory review about the applicability of both the Playstation 3 and in particular the Cell Broadband Engine is given, before the thesis is going to be completed with proposals for advanced research topics based on the presented results.

### **1.4 Typographic Conventions**

Throughout this thesis, there are references to several programs involved in the process of creating programs for the Cell architecture, of analysing the program flow, or of improving the performance. In order to highlight these terms and to visually separate them from the surrounding paragraphs, they are set in typewriter font.

Hereby, bold face denotes parts which can literally be typed into the console such as **programs** and **--options**. Meta symbols like placeholders are set in normal weight and in angle brackets, as it is for <foobar>. The system prompt is denoted by a single **\$** sign, while internal prompts might differ from program to program. For both types, though, requests for interaction are symbolized by a rectangular cursor: **1**.

#### CHAPTER 1. INTRODUCTION

## Chapter 2

## **Sony Playstation 3**

## 2.1 History

On December 3, 1994, Sony Computer Entertainment Inc. released their Playstation video console to the Japanese market [68]. Being a newcomer on the video gaming market, Sony succeeded to displace Nintendo Corp. from their almost certain first place they still claimed with their Super Nintendo Entertainment System, and should dominate the market for quite some years. From today's perspective, two main factors can be made responsible for this change: On the one hand, Nintendo did not spend much effort to press ahead with the development of their own console, the N64, since they did not see their own position to be endangered at all. On the other, Sony very early disclosed many internal design documents towards third party game developers, such that the Playstation could quickly resort to a large assortment of available video games.

From this time on, a strong competition between Sony, Nintendo, and Sega started to flare up, and was often dubbed the *console war* by the media. To the end of 1998, Sony released its sixth generation video console, the Playstation 2, to the market [70]. Even though Microsoft started to challenge the established companies with its Xbox being published to the same time, and Nintendo contributed its Game Cube into the race, the Playstation 2 could still claim the first place in the sales statistics, and even became the most often sold video console ever. Besides the substantial hardware configuration and a large fan community, the downwards compatibility towards original Playstation games can be spot as one main reason for this success.

With the next generation of video consoles being in prospect, the managers of Sony Computer Entertainment were indeed aware of the fact that there is a lot at stake, and the success or failure of the next product to be published might bring a final decision in the competition. Nintendo did still not miss the connection and was in a good position to claim its former position as a market leader back, and Microsoft was in addition expected to improve its first attempts on this market [69].

During the past generations of video consoles two success factors turned out to be most effective ones, namely a great variety of games, and computational power. While for the first

Figure 2.1: The Sony Playstation 3 video console. Source: http://www.golem.de.

point, the existing number of old games and in particular a good collaboration with third party games developers could only be of benefit, the second criterion was a lot harder to achieve, especially since very little was known about the efforts the competitors will invest.

Due to these trade secrets, the dimensioning for the new hardware for the Playstation 3, officially marketed as PLAYSTATION<sup>®</sup> 3, was kept rather optimistic, hoping to be finally ahead of the others. The CEOs of Sony Computer Entertainment Inc. hence encouraged performances of the new processor to hit the magnitude of a factor of 1000 with respect to the current Playstation 2 chip [40].

However, this idea was soon discarded due to technical and financial limits in the construction of hardware, and in particular due to problems with the power consumption and required heat dissipation. Instead, a factor of 100 has been said to be achievable, and the research division of IBM was commissioned to aid with general support from a technical viewpoint, but also to be finally involved in the actual design of the chip. In parallel, experts from Nvidia Corp. have been called in to contribute to the layout of the graphics chipset.

## 2.2 Hardware

Though the main processor differs significantly from those built into standard PC architectures, the general design of the Playstation 3 can be considered closer to such layout than to former video consoles. External interfaces have explicitly been held compliant to common standards, like the four USB 2.0 front ports the controllers can be connected to for initial registration, or for charging. These ports can furthermore be used to connect USB mice or keyboards, which are officially supported by the firmware. In the game menu, they then replace functions elsewise assigned to the controller, and ease text input in the built-in browser window or other input forms. Components like the 2.5" 60 GB harddisk with SATA connectors are widely available in PC stores as well [50]. For online gaming and web based distribution of older or smaller video games, the Playstation 3 has a Gigabit LAN connector, by which it can be connected to the internet, as well as a wireless LAN chipset and a bluetooth transceiver.

The basis of the system is represented by the Cell Broadband Engine processor, the entirely novel design developed by IBM and Sony. Since it plays the central role for this thesis, it is

explained in more detail in course of Chapter 3. The main memory is with 256 MB rather small, in particular in context of the rather high data throughput the Cell processor can achieve. However, since it is connected to the Cell processor using eight data channels with bus clocks of 400 MHz, a maximal bandwidth of 25.6 GB/s is achieved. Memory operations can thus be performed quite cheaply, which is especially inevitable in the context of up to eight cores potentially issuing requests at the same time.

For graphics processing, Nvidia likewise developed a customized redesign for the special application in the Playstation 3. Despite of being based on the G-71 chipset, little is known about the actual specifications of this so-called *RSX Reality Synthesizer*. However, it is claimed to be clocked with 550 MHz, to work upon 256 MB of dedicated graphics memory, and to be capable of 136 shader operations per clock cycle [50]. This should it settle in about the region of the GeForce 7800 when it comes to performance, while its memory bandwidth is rather comparable to the GeForce 7600 GT. Since Sony Computer Entertainment, Inc. is a promoting member in the Khronos group speaking up for open standards, they most probably also use OpenGL ES, the embedded system variant of OpenGL, to drive this chip [41]. To connect external monitors, both composite and HDMI output is available, and the video standards 480 i/p, 576 i/p, 720 i/p and 1080 i/p are supported [54]. For the 1080 i and p formats, the maximal resolution of 1920  $\times$  1080 pixels is achieved.

A novelty in the video console sector is the included double speed slot-in Blue-ray drive, which is also capable to play  $8 \times$  DVD and  $24 \times$  CD. It represents the main input device for video games, and is extended by the internal hard disk, which can be filled with games from online sources, as well as by a multi card reader. Furthermore however, the Blue-ray drive can also play videos distributed on any of the supported media types, and a software media player included in the firmware supports several container formats and video compression standards [50]. This makes the Playstation 3 also a cheap alternative to dedicated Blue-ray player devices, since the video console is subsidized by game sales.

The peak power consumption is reported to amount to 192 W, and even when it is idle, an average power of 160 W is consumed [50]. This is a lot compared to other consoles like the Nintendo Wii, and is in the range of high-end multimedia desktop PCs.

### 2.3 Scientific Interest

Despite of its advanced technical configuration, the Playstation 3 failed so far to maintain its predecessor's position on the market. Being promoted for a long time, the development of the Cell processor and its embedding into the surrounding system design retarded the actual release on the Japanese market to November 11, 2006 [69]. Surprisingly, the Nintendo Wii being released at the same time could recapture the market by improved gameplay and human interaction interfaces, rather than by pure performance.

Nevertheless, the Playstation 3 is still very widely used as a multimedia center, but also for scientific computing: The Cell processor found its way onto devices exterior to the Playstation 3 since, because IBM also markets it built onto so-called *blades*, a compact construction form for highly performant computation hosts. Being significantly more expensive than the

subsidized Playstation 3 however, latter is broadly being used for experiments with the Cell architecture, in particular in non-profit applications like for university research projects.

In this context, several works have already been published, like implementations of the Fast Fourier Transform [71], clustering of several Playstation 3 consoles for experiments with dense and sparse linear algebra [18], a ray tracer implementation [7], or partial differential equation based video compression [44]. In context of this thesis, the suitability with respect to the Optical Flow problem is inspected in more detail.

## **Chapter 3**

## **Cell Broadband Engine**

### 3.1 History

During the first considerations about the new processor, the research division of IBM soon began to stake out the possibilities and limitations with respect to both the requested performance, but also with respect to the production cost, since a too high prices potentially endanger the success of a device designed for the the adolescent clientele. While it was always clear to the designers that single core solution will hardly fulfill the performance specifications, the actual layout of a potential multi core setting has been substantially discussed about.

Until then, common concepts have already included symmetric multi core settings, this means such with equally designed cores, but to meet performance, production cost, power consumption, and heat dissipation requirements, it was soon clear that traditional architectures do not suffice for this purpose. Many modern video games need noticeably accelerated computations rather than advanced multi-threading concepts traditional settings provide. Correct game physics, particle clouds, or the simulation of fluids or nature are only some examples for such resource-intense applications nowadays widely spread in many games. On the other hand, they are too variable in their actual hardware requirements, such that a pure special-purpose layout did not come into consideration as well. In addition, Sony not only sees its new generation video console to be a pure gaming station, but should also be useable as a media center (cf. Section 2.2), and the processor should hence be capable of realtime media processing as well.

All these considerations finally lead to a fundamentally new design incorporating both traditional components as well as hardware optimized for special purpose computations. The actual development of this new chip has been taken charge of by a consortium consisting of Sony Computer Entertainment Inc. (SCEI) as the content provider and principal, International Business Machines Corp. (IBM) being responsible for the chip design, and finally Toshiba Corp. as a development and high-volume manufacturing technology partner [40].

#### CHAPTER 3. CELL BROADBAND ENGINE

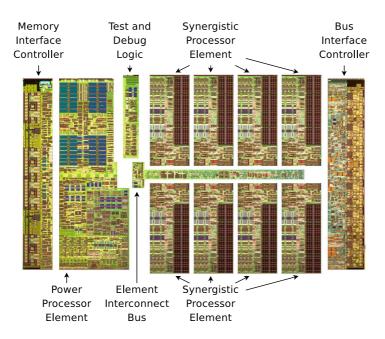

Figure 3.1: The Cell Broadband Engine Processor in an exploded view, structured by its most important features. Source: Based on a picture from http://mnagano.wordpress.com/.

### 3.2 Layout Overview

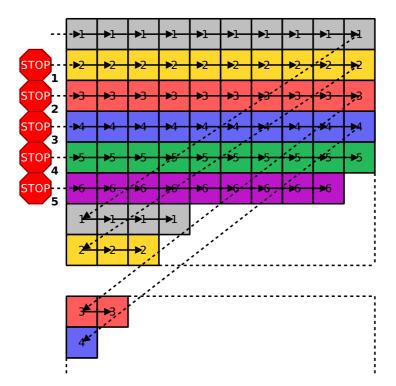

The Cell Broadband Engine is an asymmetric multi core processor with nine cores, whereof eight can be regarded as special purpose hardware. It builds up on a 64 bit hyper-threading enabled PowerPC core, called *PPE*, and is clocked at 3.2 GHz, being designed to run the operating system (cf. Figure 3.1). In section 3.4, it will be further discussed. This PPE is extended by eight 'synergistic' cores optimized for number crunching, but each only capable of one dedicated thread, a so-called *SPU kernel*, to be run. They hence strike a balance between traditional sequential architectures and special purpose hardware, while keeping the range of applications as wide as possible. Section 3.5 will explore these *SPEs* in detail [34].

All cores are extended by memory flow controllers and connected to a ring bus, the socalled *element interconnect bus* (EIB) (cf. section 3.6), which also attaches to the RAM and IO controllers (cf. sections 3.7 and 3.8).

In course of this thesis, a Linux based operating system has been installed on the Playstation 3 to use it for scientific computing (cf. Chapter 4). Unfortunately, out of the eight SPEs on the Cell used in the Playstation 3, not more than six are accessible under Linux. One of the two spare SPEs is blocked due to economic reasons, because Sony likes to keep the option open to build defective chips into the Playstation 3 consoles [50]. Such faulty chips are quite common when they are produced on wafers, since during photolithography, structures under greater incidence angles are usually subject to aberrations. Thus, chip manufacturing becomes more imprecise the further the chip is located away from the center of the wafer, and typical

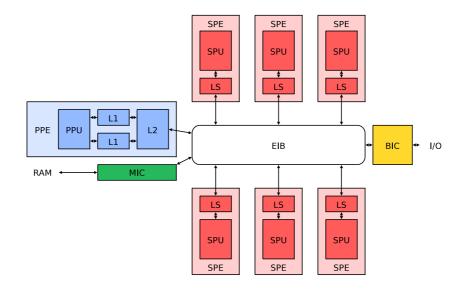

**Figure 3.2:** Block diagram of the Cell Broadband Engine Processor as it is visible on the Sony Playstation 3 running Linux.

consequences are for instance that faulty chips cannot be run on the intended frequency. If such error affects only one SPE, which is quite probable comparing the aerial fraction of the whole Cell processor, this SPE can just be turned off and though the chip can no longer be sold for IBM's blades, it is still applicable on the Playstation 3. As a side effect, both power consumption and heat generation can be reduced by a noticeable factor.

The second deactivated SPU is actually available in in the shipped firmware, *Game OS*, and can thus be assumed to work, but is nevertheless blocked in Linux. It is reported that this comes from it being used by the internal hypervisor, of which software components are permanently running in the background [25]. Details about the hypervisor and its functionality are described in chapter 4. Figure 3.2 shows a block diagram of the Cell Broadband Engine, restricted to the visible parts on the Sony Playstation 3 under a third party operating system like Linux.

It should again be emphasized that these restrictions are however only present on the Playstation 3. On products released for the high performance market, like IBM's Cell blades, all eight SPUs are available for computation, and development tools officially provided by IBM assume this situation as well.

### 3.3 Pipelining

All cores of the Cell processor follow the so-called *pipelining* concept, an effective constructional concept of basically all modern processor architectures. However, since particularities in the way this concept is implemented immediately affects the style and performance of programs throughout this thesis, a short excursion to this topic is going to be presented at this point, before detailing on the various components of the Cell Broadband Engine.

In modern processors, the execution of commands is arranged in several distinguishable stages. Each of these stages is processed within exactly one clock cycle, works upon data residing in inter-stage registers and writes its own results to the input registers for the next level where they are then waiting for being triggered by the next cycle. Even though this implementation consumes many clock cycles for one single instruction, there is usually no way around it because of data dependencies related to the memory or the general purpose register set.

However, many unbranched programs offer an opportunity to reduce the amortized amount of time one instruction needs by a significant factor, exploiting missing dependencies between subsequent instructions and the property of the single stages to be run in parallel. While one instruction is in a later stage, another can already be started in the first one without interference. Even though the delay of one single instruction cannot be reduced this way, the running time of a sufficiently long program does in fact converge to almost one clock cycle per instruction. This principle is called *pipelining*.

The execution time of any instruction can hence be divided in two parts, namely the residual time in one stage, which also equals the average time any instruction takes to be executed under the assumption that the pipeline is full, and the *latency* which is made up by the sum of remaining residual times. From a software developer's view, this means that any instruction at first glance needs its plain execution time plus latency to pass through the pipeline. By clever scheduling however, the latency of one instruction can already be used by other independent instructions to get started, and can in the ideal case be entirely compensated thereby.

Unfortunately, this simplified view of the program flow made so far can hardly be established in real programs, which are seldomly linear and built from independent instructions. Though, it is always possible to stall the pipeline to wait for any dependency to be fulfilled, which therefore builds a backup solution to the non-parallel execution whenever it is required. Several problems can even be resolved without stalling the pipeline and are hence a common approach in most modern processors.

A so-called *forwarding logic* allows some intermediate results of any stage to be fed back into earlier stages of the pipeline and hence to be used for succeeding instructions even before they are actually written back into the general purpose registers. Because instructions would normally receive their inputs from the preceding unit, the forwarding logic is in particular meant to catch all resulting deviations from usual program flow and to handle all special cases accordingly, such that the resulting execution process remains consistent to the nonforwarded version of the run. Looking closer to the pairs of stages potentially providing and requesting intermediate results, the total number of those combinations often grows faster than polynomial to the number of stages, which renders the forwarding circuit to become a non-negligible part of the processor layout. However, it is nevertheless extremely worthwhile, since it is in terms of the Cell processor able to reduce the latency of instructions from 22 clock cycles down to two to seven cycles, and thus offers the compiler a greater chance to find independent instructions to be scheduled in between for high performance.

On the other hand, conditional jumps within the program cannot be handled as effective

in a pipelined setting as it would be in a sequential one. As soon as a so-called *branch* is actually evaluated, its describing instruction is already residing in a relatively low stage of the pipeline. Following the considerations above, succeeding instructions were already to be inserted into the pipeline. This is a problem however, as choosing any of the two possible branches can reveal to be incorrect when the branch is finally evaluated, thus forcing the processor to reject all instructions already started from the wrong branch and to start again with the correct one. Such scenario is referred to as *branch misprediction* and a still a frequent performance problem on modern processors. Paragraph 3.5.4 goes into more detail on this issue.

### **3.4** Power Processor Element

The *Power Processor Element* (PPE) is the main core included in the Cell Broadband Engine chip. Designed for running the operating system, it is fully compliant to 64 bit PowerPC processors like they are built into earlier Macintosh computers manufactured by Apple, Inc. It consists of a POWER Processing Unit (PPU), and a traditional cache hierarchy consisting of two 32 kB L1 instruction and data caches, as well as a joint 512 kB L2 cache [19]. The L2 cache connects with 25.6 GB/s bandwidth up- and downstream to the Element Interconnect Bus (cf. Section 3.6), and with 51.2 GB/s in both directions to the two L1 caches. Latter are eventually connected to the PPU using a bus capable of a bandwidth of 51.2 GB/s.

Because PPU and PPE are hard to distinguish from software side, since the cache hierarchy is hidden to the programmer, both terms are often referred to as synonyms. In fact, even the official documentation published by IBM and Sony is inconsistent in this point, in particular when it comes to rather software-related issues [29].

#### 3.4.1 Architecture Overview

The PPU provides two pipelines for interleaved multithreaded computation of synchronous threads, but processes both locally in-order. This means that it does not perform optimized reordering of instructions as this is done in other modern processors [40]. As a result, the pipeline length could be restricted to 23 stages, while instantly reducing the residence time in one stage by about a factor of two compared to earlier designs. These 23 stages divide into six stages for instruction cache and buffer, six for instruction decode and issue, and finally eleven instruction type specific backend stages.

Since this model can be seen as a two-way multiprocessor with shared dataflow, it presents itself as a dual-core processor towards the operating system. Each of these threads can access a 32 element 64 bit general purpose register, a fixed point unit, as well as a load and store unit. A floating point unit extends this setting by a decoupled pipeline for vector and floating point operations, which is designed on a 128 bit wide dataflow. It owns a 32 times 128 bit register file, and can operate on vectors of varying element width, such as  $2 \times 64$  bit,  $4 \times 32$  bit,  $8 \times 16$  bit,  $16 \times 8$  bit, or  $128 \times 1$  bit. By processing a whole vector at once, this architecture hence offers the opportunity to use a way of instruction level parallelism besides standard sequential

implementations. Details on these so-called *SIMD* extensions are more important in context of the SPUs and are described there (cf. Paragraph 3.5.3).

#### **3.4.2 PPU as an Application Controller**

Regarding the role of the PPU with its partition of the overall computing power the Cell processor supplies, it is soon clear that it is mostly concerned with running the operating system, and in particular also the graphics engine, which needs to be entirely emulated in software (cf. Section 4.1). However, its prioritized position with respect to explicit access to the RAM enables it for another important application.

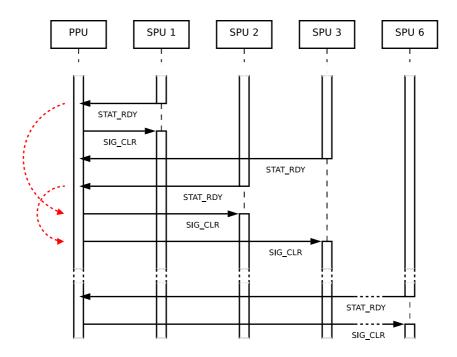

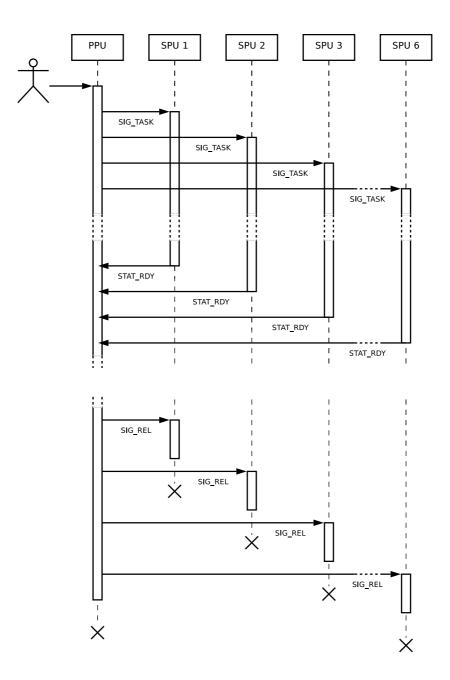

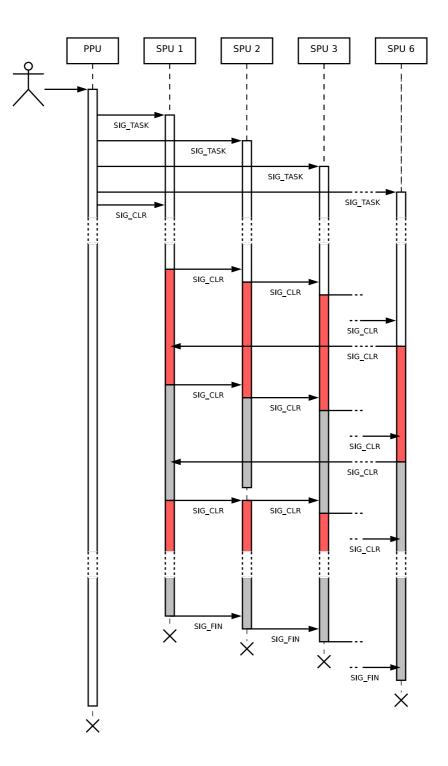

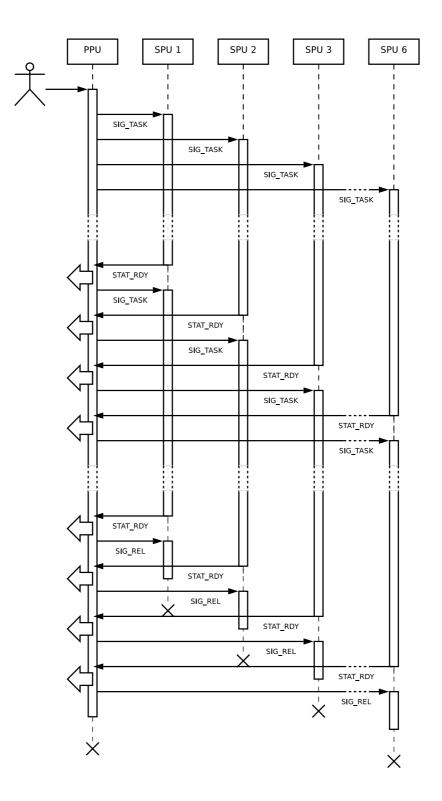

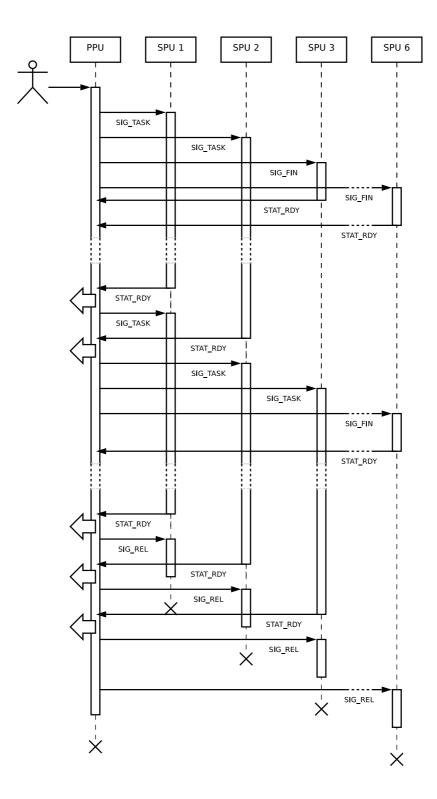

When a program is executed by the operating system, it is for the time being a pure PPUbased task. At runtime, the SPU kernels are then sent to their destination and memory is allocated from PPU side. The PPU is thus always aware of the entire memory load allocated in RAM, and also manages these amounts based on information and requests from the SPUs. Therefore, also the means for synchronization available in the Cell chip are partly PPU-oriented, i.e., synchronization among SPUs primarily takes place by using the PPU as a relay station. These methods are detailed in Section 3.5.6.

This way, the PPU can be regarded as an application controller not only dispatching and collecting SPU threads when a program is started or terminated, but also taking care of necessary synchronization between SPUs, managing allocated memory blocks, and even providing active scheduler capabilities if sophisticated scheduling by means of trigger messages is required at some point. Though it typically does not immediately participate in computations, it still forms both reference clock and memory management unit, and provides the user interface by means of graphical output and system interaction.

Anyway, as experience shows, the actual distinction of jobs better to be assigned to PPU, and those more applicable to the SPU is sometimes nontrivial and can cause severe problems. For instance, if data to be read by the SPUs resides in the PPU's L2 cache, the Memory Interface Controller (MIC) redirects access on this information to the PPU's L2 cache, and bursty traffic can exhaust the PPU's own link to the EIB [48]. In course of this thesis, some of these problems are discussed in more detail (cf. Paragraph 6.4.4).

### 3.5 Synergistic Processor Element

In contrast to the PPE being eligible for complex multithreading purposes, SPEs are designed for pure arithmetics. Hence, they are no traditional multi-purpose core, but represent a compromise of this type and a special purpose architecture.

The instruction set used is still very close to the PPE correspondent, and the general structure of programs does at first glance not need to be modified too much in order to compile it for an SPE. On the other hand however, several novelties in the architecture cause mandatory extensions in the program flow, and in order to make use of the full performance provided by these cores, a considerable amount of manual work is inevitable. Details of these differences to be paid regard to are discussed in the next paragraphs. Like for the PPE, SPEs consist of a processor unit called *Synergistic Processor Unit* (SPU) extended by a Memory Flow Controller (MFC) and a cache called *Local Store* (cf. Paragraph 3.5.2). Because the difference between SPU and SPE is primarily founded in a constructional view and can hardly be distinguished from a software side, these two terms are in literature often used as synonyms.

#### 3.5.1 Architecture Overview

The SPUs are designed to compute natively on 128 bit wide SIMD vectors [19]. For this purpose, they are equipped with a 128 times 128 bit general purpose register file. This is either used by 128 bit vectors homogeneously splitted into various element types, or by scalars which reside in the cells aligned to the most significant bits [31]. In latter case, all remaining SIMD slots are filled with meaningless values.

Computations upon these register contents are performed by two execution pipelines, often referred to as odd and even. The even pipeline contains both the Fixed Point and the Floating Point Unit, and is thus designed for arithmetics. Simple integer operations therein are said to have two cycles of latency for dependent values, single precision operations six, integer multiplications and conversions between integer and float values seven [11]. All those operations take one cycle to execute, such that by intelligent scheduling of independent operations, the latency gap can be bridged by some other instructions. Double precision arithmetics are more expensive, since they cannot be fully pipelined and hence need seven clocks, besides introducing an additional latency of six clock cycles. They are thus about one order of magnitude slower than single precision computations and should be avoided whereever possible. To be nevertheless able to yield results with highest possible effort, several approaches can be found in literature proposing to apply iterative refinement strategies, like the approach of Langou et al. [45]. The main idea behind such mixed precision strategies is to compute on single precision values as long as this does not deteriorate the results too much, and to finally refine these intermediate results in double precision. This way, results are reported to be achieved about ten times faster than computations entirely performed in double precision, by keeping the accuracy constant.

The odd pipeline in contrast consists of the Permute, the Branching, the Channel and the Local Store Unit and thus covers the nonarithmetic part. They perform loads and stores, branch hints, channel operations and Special Purpose Register (SPR) moves with six, and all remaining operations with four cycles of latency. The actual execution time of any of these operations takes one additional cycle, each. The division of both pipelines allows to process a pair of odd and even instructions synchronously, i.e. one value can be fetched from the Local Store (cf. Paragraph 3.5.2), while another is currently being processed.

Information about this special configuration is worthwhile, since it enables the programmer to react on this situation by applying optimizations towards a minimization of latencies. Throughout this thesis, this concept is used several times, since it allows to speed up processes just by arranging for a balance between odd and even instructions (cf. for instance Section 6.5.2). By *channels*, SPUs communicate with other elements on the ringbus. From a hardware perspective, channels are unidirectional links between the SPU and external devices, like the SPE's MFC, and are to a certain degree buffered. This buffer is called the capacity of the channel and describes how many entries can be written at once before further writes are stalling and are thus introducing latency. Reading is always blocking if no data is in the channel [33].

Since all non-local operations like DMA requests or inter-core communication control is performed via dedicated channels, meaningful aliases for those specific calls are provided by libspe2. Paragraph 3.5.5 goes more into detail about these intrinsics.

#### 3.5.2 Local Store

Random Access Memory (RAM) is a typically volatile storage technology being applied in most modern computer systems. It is significantly faster than for instance hard disk or remote network resources and returns queried data sets in constant time, this means independently from the position they are stored at, or from their relation to the last set requested. Unfortunately, RAM is also a lot more expensive in production cost and space consumption compared to mass storage devices of equal capacity. Along with the fact that it is eventually erased as soon as the power supply is disrupted, RAM is seldomly used exclusively in a system, but can often be regarded as a cache for the data contents stored on hard disks.

Data needed to compute upon as well as the program itself is copied into the RAM, from where it can then be comfortably accessed. Does the physical capacity not suffice, the hard disk is often still used as a slow backup solution. In terms of memory management, this process is called swapping and nowadays handled in dedicated hardware cycles.

Unfortunately, the modern RAM technology is still quite slow in response and transfer times compared to the speed processors can be run at, which would immediately lead to stalls on open memory requests. This is bad, since typical program characteristics often involve more than one access to a certain variable within a short time span, this means, within a local neighborhood of instructions processed. The memory hierarchy is therefore continued in even faster, but still significantly smaller intermediate levels of caches caches residing on the processor chip itself, and the general purpose register file can be regarded as the fastest, but also smallest unit within this hierarchy.

Parts of this hierarchy are shared by all computational kernels on the different SPUs, as well as by the operating system kernel running on the PPU. Besides any external or internal mass storage media, this holds in particular for the RAM which is also the lowest instance providing shared memory access for different kernels to the same resources. In addition, each processor core is equipped with an own dedicated cache used for intermediate results and fast working copies. On SPU side, these caches are called *Local Store* and have an overall capacity of 256 Kilobytes, which covers both instructions and data being used by the kernel.

This concurrent design is not only one major argument for the performance gain possible to achieve for several programs by porting them from any traditional to this architecture, it also introduces several potential hazards known from multi-threaded software design on conventional computer systems. These are on the one hand so-called race conditions in the narrower sense, describing the necessity to synchronize concurrent access to the same resource such that operations are performed on it in order. But even for independent writing access to a certain memory cell, as it might hold for separable problems, it is inevitable to find a suitable coordination such that results developed by one kernel do not interfer with those written out by another, i.e. that the whole setting remains consistent at any time.

Therefore two main aspects need to be considered at any time, namely availability and validity. While the first term describes the fact that data to be accessed needs already to be loaded into the cache beforehand, latter refers to the version of these data sets with respect to changes performed by other cores.

This problem is also known from traditional architectures, and is in this context solved by a hardware logic. In such conventional managed caches like the one implemented in the PPU, vectors of validity information are kept alongside the cached memory lines to distinguish 'dirty' lines, i.e. such not synchronized to RAM yet, from 'fresh' ones. Whenever a line is requested, the circuit then decides whether the memory line is still valid in cache, and provides the cached version, or fetches the respective line from RAM first. Unfortunately however, this logic works without any knowledge of the algorithm being executed, and does hence not know anything about its characteristics and access frequencies to certain values. It might hence happen that a line is being moved out of the cache, just before it is then going to be used again a few cycles later. On the other hand, lines not to be used again can reside for too long in the cache, thereby keeping other lines from being handled more efficiently. In such situations, managed caches can introduce a high overhead in both time and memory bus usage.

Since the PPU needs to assure categorical conformity with the existing PowerPC specification, it necessarily also needs to rely on a managed cache hierarchy. Meanwhile however, chip designers have not been bound to any of these conventional criteria when creating the layout for the SPUs. To enable programmers to accelerate their software on this distributed architecture and to avoid unoptimal cache situations like described above, they made any transfer of data between RAM and the Local Store explicit. Only instruction fetch, which is uncritical because the program flow can easily be planned and foreseen at any point, is still performed by a circuit.

This allows for very efficient programs, since the programmer can decide at any point which values are meant to reside in the cache, and which are not. More importantly however, developers can already request memory lines, when they are not needed yet, such that they are available when the first request to them is going to be scheduled. A drawback of this method is however, that the entire responsibility over memory management and in particular also data synchronization is inflicted to the programmer, independent of how trivial or how time-uncritical an operation might be. This means that even for operations without performance requirements, any memory interaction needs to be explicitly modeled. This issue can not only expand the programming code significantly and deteriorate its general appearance and lucidity, but can thus also be a potential source of error.

Meanwhile, the Local Store still remains a cache immediately interacting with the Memory Flow Controller, which coordinates access to the physical RAM on a low level basis. In particular, all transfers of data in between these two components must be ensured to be compliant with respect to memory word alignment:

Alignment means in this context that both the address and the length of the data block handled must be being a multiple of 128 bits, both in RAM and Local store. This results in the addresses and length specifications to end on a series of at least 4 zeroes in binary representation:

$$128\mathbf{b} = 128\mathbf{b} \cdot \frac{1\mathbf{B}}{8\mathbf{b}} = 16\mathbf{B}, \quad \log_2(16) = 4.$$

This principle is commonly used on almost all architectures and allows for larger addressed storage while still keeping addresses in the range of the maximum bus width supported by the processor. This way, tailing zeroes can be easily made implicit and the released digits can thus be used for a higher range of values possible to process.

Unlike most processors, where correct memory alignment is automatically ensured by hardware circuits and invisible to the programmer, special assembly and high level instructions need to be used on the Cell processor to model these requirements in software. One example for such intrinsic for C and C++ is given by spu\_mfcdma32 provided by libspe2, which starts a reading or writing DMA access by internally mapping to a sequence of seven assembly instructions [58]. It forms the basis for most cache operations throughout this thesis. Besides others, this operation takes a so-called *DMA flag* as a parameter, which assigns a unique ID to a DMA process. Technically, it tells the MIC to set the respective bit in a dedicated 32 bit register as soon as the requested data is valid. This way, memory contents can be requested, the waiting time can then optionally be bridged by some arithmetic operations on different Local Store partitions, and finally the service register can be triggered for the loaded data to become valid.

#### 3.5.3 AltiVec SIMD

As the consequence of these considerations, issuing equal operations on potentially different data sets hence causes a high number of similarities in the state of the processor. Not only the instruction fetch and decoding phase is similar, the same holds as well for several stages in the pipeline and in particular for the forwarding logic. Processor designers use these observations to extend their architectures by a relatively simple way to speed up many programs, namely *Single Instruction Multiple Data* (SIMD) extensions in terms of Flynn's taxonomy [22].

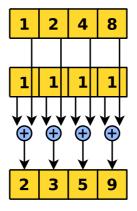

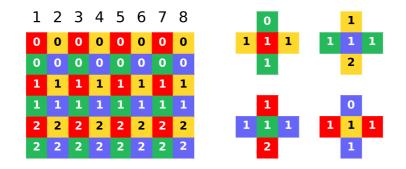

Figure 3.3 shows an example of such operation, based on integer vectors:

$(vec_int4) \{1, 2, 4, 8\} + (vec_int4) \{1, 1, 1, 1\} \rightarrow (vec_int4) \{2, 3, 5, 9\}$

Since the operation is of homogeneous structure and source and target values are residing in four adjacent memory cells aligned to 128 bits, this instruction does only need one processor cycle to execute.

Instead of working on single values only, the full bandwidth of operations is extended to a multiple of scalar data types, hence yielding vectors of a fixed number of equally typed elements. In terms of the SPUs, the width of operations is fixed to 128 bits, by offering either sixteen **char**s, eight **short** ints, four single precision floating point numbers (**float**) or four **int**s, as well as two double precision floating point numbers (**double**) and the unsigned

Figure 3.3: Example execution of a SIMD based addition of two integer vectors.

versions of the respective fixed point notations. Except for the double precision extension, this concept has already been used to enhance the performance of PowerPC architectures using a SIMD extension published under the product names AltiVec, or Velocity Engine Multimedia Extension [56, 51]. Originally designed for the PowerPC series produced by IBM and licensed by Apple to be built into the MacBook series notebook computers, the brand name AltiVec is today held by Freescale.

By making parallelism explicit, the programmer can map structural characteristics to the hardware like this has already been possible on traditional vector computers in earlier times. However, while latter computer systems were designed for much higher element counts and were thus often dedicated to special purposes, a significantly lower bandwidth embedded into a classical sequential processor layout creates a compromise between the benefits of both approaches.

Hereby, such vectors need to span in adjacent memory cells and must be aligned to 128 bits. Any instruction issued on these variables is then handled on a per-vector basis, which means that any of these SIMD vectors is in principle treated like scalar values with respect to data flow inside the processor, except for a higher bandwidth and redundant computation units where the full bandwidth is needed.

The instruction fetch and decoding stages involved in processing of such SIMD instruction do not differ between scalar and vector based operations, because the wider data width does typically not project onto a much different instruction format, as still only one single command is described by it. However, the different inter-stage registers and connecting datapaths in the execute and write back phases are indeed necessary to be adapted to the new bandwidth. To perform computations on all partitions in parallel, a sufficiently high number of integer and floating point units must additionally be provided, as well as an extended branching logic connected upstream to become capable of the different element sizes a SIMD vector can contain. Such circuit is needed to sort and split the 128 bit of width into for instance eight 8 bit wide character components, into four single precision floating point numbers, but is also needed in traditional designs to assign floating point numbers to the floating point unit, while any other data type is sent to the fixed point arithmetic and logic unit. Technically, this process typically comes down to a generation of dedicated driver signals activating or activating certain units, or setting them to a mode for the special data type to be processed.

At this point, one major difference between traditional architectures and the Cell processor becomes obvious: While in traditional architectures, SIMD vectors and scalar values are handled differently, the SPUs of the Cell processor always work in chunks of 128 bit, whereby for scalar operations, the rightmost bits are just containing unmeaningful data. This is also the reason for the Cell being marketed as a *Broadband Engine Processor*. Special assembler mnemonics and also immediate high level constructs (cf. paragraph 3.5.5) exist to manage the transitions between scalar valued and vector valued data. Switching between these is indeed very often necessary, because for instance on the one hand, many computations and comparisons on values can be performed in full width, but when it comes to decisional jumps, the branching condition needs to be accumulated as a scalar residing in the first 4 bytes.

#### **3.5.4 Restrictions**

For full SIMD support, the SPUs possess a floating point unit capable of four single precision operations in parallel, but only one double precision operation per clock cycle. Because arithmetics is always performed on full 128 bit width, double precision operations cause both double word wide halves to be processed one after the other, independent from whether the second half contains meaningful values or not. This means that even for instructions with scalar range, the second half will still be processed by the SPU, counteracting the pipelining principle: Since both halves need to be fed into the unit one after the other, arising dependency problems are solved in a straightforward manner, namely by stalling both pipelines for additional six cycles to bridge the latency between the first and the second half of the SIMD vector. This reduces the double precision performance significantly compared to single precision computations. In contrast to a single precision pipeline length of seven cycles including six cycles of latency, the double precision pipeline thus lasts 13 clock cycles, whereof again only six can be reused by other instructions. It is hence always advisable to fall back to single precision whenever it is possible, or to use mixed precision approaches (cf. Paragraph 3.5.1).

Besides the lower accuracy in computation and the potential arithmetic errors arising from this fact, the SPU floating point unit does not completely support the IEEE floating point specification, which introduces further errors. In particular, it only supports round-to-zero from the rounding modes specified in the IEEE 754 standard, which is tantamount to truncating the binary representation to the maximal length of the mantissa [30]. This restriction is not imposed to the double precision computations which support the full range of IEEE rounding modes, and only partially applicable to the PPU, supporting both round-to-nearest mode and an emulation mode for SPU accuracy called *graphics rounding mode* [58]. For single precision computations on the SPU however, this deviation affects many C math library functions like floor, exp or log, which finally renders arithmetic results only to approximate the more exact solutions yielded on a x86 based CPU, or the PPU.

Furthermore, the conception of the SPU SIMD extension implies the special values *not* a *number* (NaN) and *infinity* (Inf) to be handled like normal numbers, this means like the

number their internal representation would suggest. Because all operations on the SPU are performed in SIMD, this again applies to all single precision floating point arithmetics and can introduce further inconsistencies if relevant special cases are not caught in software.

In paragraph 3.3, the performance problem related to branch mispredictions has already been mentioned. In particular, any mispredicted branch causes the speculated branch to be entirely flushed from the pipeline, thus introducing a penalty of approximately 20 cycles [30]. Most modern processors hence possess a branch prediction mechanism by means of hardware lookasides like branch history tables, branch target address caches, or branch target instruction caches. Unfortunately, the SPUs does not utilize any of these techniques, but instead relies on a programmer directed branch prediction. Hereby, the branch speculation is already established at compile time, whereby the speculation later assumes unbranched, i.e. linear continuation of the program at the respective points, if no definite hint by the programmer has been carried out. Developers can hence make use of several remedial measures to reduce mispredicted branches.

The most effective way to do so is certainly to reduce branching to a minimum, by application of techniques like loop unrolling, function inlining or select bit instructions [49]. For loop unrolling, several iterations of a loop are performed one after the other without intermediate branches. In program code, this implies an instruction in the loop body to be coded several times with adapted parameters, while contingent loop counters are always increased by the degree applied. Function inlining means that a function does not allocate a frame on the stack, but the body is embedded into the calling routine at compile time, allowing for both easily readable code and highly performant running behaviour. Select bits instructions are finally a hardware assisted way to entirely avoid branching for particularly short branches, namely by computing both branches towards intermediate results, independent from which branch is actually referred to and then selecting the one intermediate result that would actually be computed if the branch was taken. Latter can be done with a single logic operation and is represented by the selb assembly instruction. Of course, this concept only pays off if the time it takes to unconditionally process both ways is still shorter than the expected value for the average loss due to branch mispredictions.

Loop unrolling has a second accelerating effect to the program: Since floating point operations are typically associated with latencies of six cycles, five independent instructions should be scheduled in between two dependent instructions, since these cycles are otherwise allowed to lapse [50]. By a loop unrolling approach with a sufficiently high assortment of independent instructions in the loop body, the compiler can reorder these instructions in a way that they are interleaved and hence use latencies most efficiently.

A second way to reduce the overall number of mispredicted branches is to influence the order conditionals are evaluated, since the processor is designed to assume that always the first branch would be taken. While this is indeed an option for programs written in assembler code or included into the high level language as such, it can cause quite unpredictable behaviour during the code generation, if the software is entirely written in a high level language like C. Depending on the compiler and its optimizations made, the order of independent code fragments can still be shuffled, thus reverting the improvements made by the developer.

#### CHAPTER 3. CELL BROADBAND ENGINE

To circumvent this behaviour, compilers offer so-called *branch hint instructions*. Here, the programmer can specify what he anticipates the conditional expression to evaluate to, such that the compiler can reorder the branches accordingly. Due to this predefinition at compile time, these instructions are typically referred to as *static* branch hints, distinguishing them from hints evaluated at runtime. Latter are also supported by the SPU, but only if they are explicitly embedded into the program code, represented by the hbr assembler mnemonic family. Their own execution needs one cycle and they must at least be placed 19 instructions before the branch is executed, such that the core has enough time to react on this specification. As soon as this manual prediction is correct, penalty-free branching can be ensured. At the same time, a 20 cycles misprediction penalty is imposed on the contrary branch, such that cautious deliberateions at design time are valuable.

Comparing the whole concept of the Cell Broadband Engine to traditional symmetric multi-core processors, the specific design of the SPU implies an entirely different programming style. Even though this fact forms the main argument for the Cell and also explain its fame as an object of research, it should also be mentioned in this section, because programs are in general not as easy portable to this platform as they are to many others. Besides a completely different binary layout which is pointed out in more detail in section 3.9 and a new instruction set for the SPUs, several other aspects underline the pure number crunching objective of the whole SPU design. They are for instance not multithreading enabled and can also not immediately be triggered by the BIOS, thus making them dependent from an operating system running on the PPU. Because the program kernels are always entirely transferred into the Local Store, the SPUs are also fundamentally useless as coprocessors to run system tasks which are typically very bursty in resource allocation and therefore heavily shuffled with other background tasks. However, as soon as a dedicated system task can be identified to be very computation intensive and permanently running, as it might be the case for digital signal processing implementations, this task can be formulated in terms of an SPU kernel and swapped out to one single SPU. Even though this SPU would then no longer be available for joint computations, this method can indeed be worthwhile, because these dedicated processes are typically less constraint to synchronization with the rest of the processor, and can hence be assumed to run with high performance.

#### **3.5.5 SPU Intrinsics**

Programming the SPU in a high level language needs to meet different requirements than writing programs for a traditional processor. While for x86 based architectures, branching does not play as an important role and an explicit cache management is at best marginally touched by means of software design patterns, like those optimizing for the cache direction in multidimensional data sets, such considerations are indeed necessary when developing for the Cell, and in particular for one of the SPUs. To be capable of these new machine-dependent features, SPUs do not follow an established instruction set specification, but implement a new restricted instruction set, which shows strong similarities to the instruction set used on the PowerPC platform [32, 33].

Conspicuously, arithmetic and logical operations are always designed to have a scope of

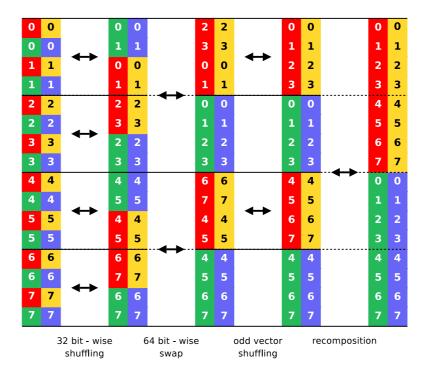

the full SIMD vector and therefore replace their scalar counterparts in other assembly languages. In addition, special instructions model data transfers between the leftmost vector entry and the remaining slots, to convert between explicitly scalar and vector-based applications, or shuffling applications. In principle, latter are nothing more than a natural extension of bitwise logical operations on traditional hardware to a 128 bit width, though working on a greater atomic element size. They are helpful for a fast reordering of single bytes whenever across-slot movements need to be performed, and can be combined with conventional bitwise operations to achieve a finer granularity. In Paragraph 6.5.2, these instructions are applied to a concrete example.

In particular, while operations like cyclic shifts still exist on a per-value basis, byte shuffling can be used to move bytes over element boundaries and hence overcome the problem of alignment issues. Without these techniques, operations between two different elements in the same vector could just not be performed at all, since there would be no way to align both values in the same bit range of the processing unit.

However, the increased bandwidth is not the only extension to be considered with respect to the new instruction set. Moreover, the situation of joint computing on SPUs as a pre-stage of special purpose hardware requires an additional group of commands to be implemented as well. Besides control over the memory flow controller taking care about RAM accesses and Local Store management, various synchronization techniques must also be addressable from the software side. These operations are actuated by channels that can be written to or read out, while reading access can be set blocking to wait for an external synchronization or memory event to happen.

Constructing compilers for this setting, one has to be aware of the fact that most convenience accommodations to the programmer come along with performance losses, which holds in particular for the adaption of existing sequential languages to this architecture. On the other hand, it is always desireable to fall back to widely spread languages, to profit from synergy effects from the community and to increase acceptance among developers. In past times, this issue has often been addressed by means of inline assembly code, this means the high level language is indeed used to describe the general program flow, but whenever a resource critical functionality is needed, it is immediately coded in embedded assembler mnemonics. In practice, this technique often leads to whole routines being entirely written in assembly language to ensure a high performance, which can render work to be tedious due to the missing support of loops and other high level structures.

The designers of the SPU development kit abstracted from this problem by giving the programmer high level commands at hand which are guaranteed to immediately map to a dedicated assembler instruction. These special functions are called *SPU intrinsics* and hence fill the gap between actual low level programming and modern, widely spread languages like C or C++. They are extended by a variety of other new commands mapping to a sequence of, instead of only one, assembly instructions. Because both types are quite equal in usage regarded from an application developer's point of view, they will not be further distinguished in the course of this thesis. By including spu\_intrinsics.h into the program source code, the SPU specific extensions are introduced to the framework.

#### CHAPTER 3. CELL BROADBAND ENGINE

Making the internal data structure explicit, declaration of data types has been extended by several new SIMD vector data types, while scalar values can still be used. The most common vector types in this context are  $vec_float4$ , consisting of four single precision floating point numbers, and  $vec_int4$  being constructed out of four concatenated integer values, as the name suggests. One should however always be aware of the fact that scalar types will be fetched into the first few bits of a 128 bit register and internally processed as a vector with three unmeaningful entries, whereas vector types are explicitly handled as such and are always fetched vector-wise. The compiler observes this difference by means of typechecking and does not allow implicit casts between both interpretations.

In paragraph 3.5.2, the special alignment of data to be synchronized with RAM contents has been outlined. This requirement needs to be heeded all time when allocating storage in the Local Store. For dynamically allocated memory, \_malloc\_align can be used to ensure this fact, while the compiler's alignment attributes have the same effect on local variables. For instance, the following sample code fragment allocates two integers aligned to  $2^5 = 32$  Bytes, one of them dynamically and one statically:

```

int *dynamic_int = (int*)_malloc_align(sizeof(int), 5);

int static_int __attribute__ ((aligned (32)));

```